Rev. 9.0, 8/2012

# Switch Mode Power Supply with Multiple Linear Regulators

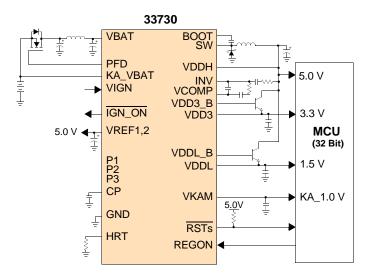

The 33730 is a multiple output power supply integrated circuit for automotive applications. The integrated circuit (IC) incorporates a switching regulator, which operates over a wide input voltage range from 4.5 to 26.5 V.

The step-down switching regulator uses a fixed frequency pulse-width modulation (PWM) voltage mode control. It has a 3.5 A current limit (typical) and the slew-rate is adjustable via a control pin to reduce switching noise. The switching regulator has an adjustable frequency oscillator, which allows the user to optimize its operation over a wide range of input voltages and component values.

The linear regulators can be configured either as two Normal mode regulators ( $V_{DD3}$ ,  $V_{DDL}$ ) and one standby regulator ( $V_{KAM}$ ), or as one Normal mode linear regulator ( $V_{DDL}$ ) and two standby regulators ( $V_{KAM}$  and  $V_{DD3}$  Standby). Two protected outputs [VREF (1, 2)] are used to provide power to external sensors.

#### **Features**

- Provides all regulated voltages for Freescale 32-bit microcontroller family

- Adjustable frequency switching buck regulator with slew-rate control

- Power sequencing provided

- Programmable voltages V<sub>DDL</sub>, V<sub>DD3</sub> 3% accuracy

- Programmable standby regulator V<sub>KAM</sub> 15% accuracy, operating down to 4.5 V at the KA\_VBAT pin

- V<sub>DD3</sub> can be programmed as an optional second standby regulator with 15% accuracy

- Provides two 5.0 V protected supplies for sensors

- Provides reverse battery protection FET gate drive

- · Provides necessary MCU monitoring and fail-safe support

# 33730

#### **SWITCHING POWER SUPPLY**

EK SUFFIX (PB-FREE) 98ARL10543D 32-LEAD SOICW-EP

| ORDERING INFORMATION                                                                   |                        |             |  |  |

|----------------------------------------------------------------------------------------|------------------------|-------------|--|--|

| Device (Add R2 Suffix for Tape and Reel)  Temperature Range (T <sub>A</sub> )  Package |                        |             |  |  |

| MCZ33730EK                                                                             | -40 °C to 125 °C       | 32-SOICW-EP |  |  |

| MC33730EK *                                                                            |                        |             |  |  |

| * Decemmended d                                                                        | avias for all pave das | iana        |  |  |

\* Recommended device for all new designs

Figure 1. 33730 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

# **DEVICE VARIATIONS**

# **Table 1. Device Variations**

| Part no.   | Temperature Range | Description                                   |  |

|------------|-------------------|-----------------------------------------------|--|

| MCZ33730EK | -40 °C to 125 °C  | Reset detect circuitry                        |  |

| MC33730EK  | -40 C to 125 C    | Improved VDDL and VDD3 reset detect circuitry |  |

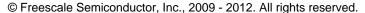

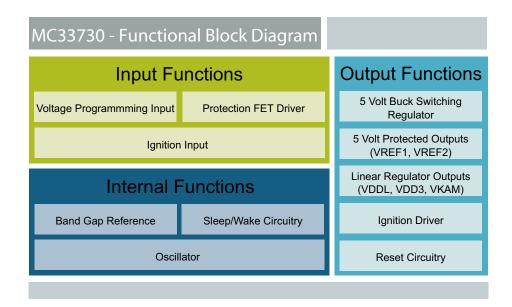

# INTERNAL BLOCK DIAGRAM

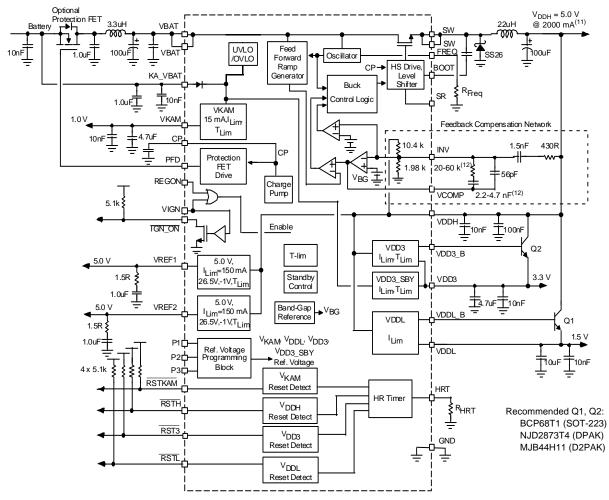

Figure 2. 33730 Simplified Internal Block Diagram

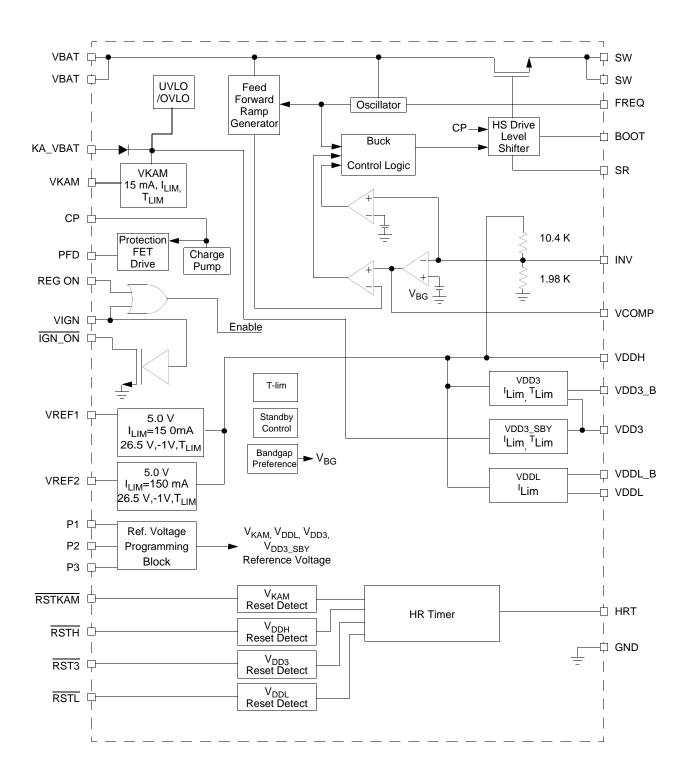

# **PIN CONNECTIONS**

Note: The exposed pad is electrically and thermally connected to the IC ground.

Figure 3. 33730 Pin Connections

Table 2. 33730 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 12.

| Pin Number | Pin Name | Pin Function           | Formal Name                  | Definition                                                                                                                            |

|------------|----------|------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1          | HRT      | Analog<br>Output       | Hardware Reset Timer         | This pin is the hardware reset timer programmed with an external resistor.                                                            |

| 2          | RSTKAM   | Open Drain             | VKAM Reset                   | This pin is an open drain reset output, monitoring the $V_{\mbox{\scriptsize KAM}}$ supply to the microprocessor.                     |

| 3          | RSTH     | Open Drain             | VDDH Reset                   | This pin is an open drain reset output, monitoring the $V_{\mbox{\scriptsize DDH}}$ regulator.                                        |

| 4          | RSTL     | Open Drain             | VDDL Reset                   | This pin is an open drain reset output, monitoring the $\mathrm{V}_{\mathrm{DDL}}$ regulator.                                         |

| 5          | RST3     | Open Drain             | VDD3 Reset                   | This pin is an open drain reset output, monitoring the V <sub>DD3</sub> regulator.                                                    |

| 6          | VREF2    | Power Output           | VREF Output 2                | This pin is the output of the protected supply VREF2. The pin is supplied from the $\rm V_{DDH}$ through the protection FET.          |

| 7          | VDDL     | Analog Input           | VDDL Regulator               | This pin is the V <sub>DDL</sub> regulator output feedback pin.                                                                       |

| 8          | VDDH     | Analog/<br>Power Input | VDDH Regulator               | This pin is the 5.0 V output feedback pin of the buck regulator. The pin is also a power input for the protected outputs VREF1,2.     |

| 9          | VDDL_B   | Analog<br>Output       | VDDL Regulator Base<br>Drive | VDDL linear regulator base drive.                                                                                                     |

| 10         | VREF1    | Power Output           | VREF Output 1                | This pin is the output of the protected supply VREF1. The pin is supplied from the $\rm V_{DDH}$ through the protection FET.          |

| 11         | REGON    | Logic Input            | Regulator Hold On            | Regulator Hold On input pin (5.0 V logic level input).                                                                                |

| 12         | IGN_ON   | Open Drain             | VIGN Status                  | This open drain output signals the status of the VIGN pin.                                                                            |

| 13         | VCOMP    | Analog<br>Output       | Compensation                 | This pin provides switching pre-regulator compensation, it is the output of the error amplifier.                                      |

| 14         | INV      | Analog Input           | Inverting Input              | Inverting input of the switching regulator error amplifier.                                                                           |

| 15         | FREQ     | Analog Input           | Frequency Adjustment         | Frequency adjustment of the switching regulator. The value of the resistor to ground at this pin determines the oscillator frequency. |

# Table 2. 33730 Pin Definitions(continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page 12.

| Pin Number | Pin Name          | Pin Function     | Formal Name                         | Definition                                                                                                            |

|------------|-------------------|------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 16         | P1 <sup>(1)</sup> | Logic Input      | Programming Pin 1                   | Programming pin 1 for the $V_{DD3}, V_{DDL}$ , and $V_{KAM}$ reference voltages.                                      |

| 17         | P2 <sup>(1)</sup> | Logic Input      | Programming Pin 2                   | Programming pin 2 for the V <sub>DD3</sub> , V <sub>DDL</sub> , V <sub>KAM</sub> reference voltages.                  |

| 18         | PFD               | Analog<br>Output | Protection FET Drive                | Reverse battery protection FET gate drive.                                                                            |

| 19         | BOOT              | Analog Input     | Bootstrap                           | This pin is connected to the bootstrap capacitor.                                                                     |

| 20         | SR                | Analog Input     | Slew-rate                           | Slew-rate Control of the switching regulator.                                                                         |

| 21,22      | SW                | Power Output     | Switch Node                         | These pins are the source of the internal power switch (N-channel MOSFET).                                            |

| 23,24      | VBAT              | Power Input      | Battery Voltage<br>Supply           | Voltage supply to the IC (external reverse battery protection needed in some applications).                           |

| 25         | KA_VBAT           | Power Input      | Keep Alive Supply                   | This pin is the keep alive supply input.                                                                              |

| 26         | СР                | Analog<br>Output | Charge Pump                         | External capacitor reservoir of the internal charge pump.                                                             |

| 27         | VKAM              | Power Output     | Keep Alive Memory                   | Keep-Alive Memory (standby) supply output.                                                                            |

| 28         | VDD3              | Analog Input     | V <sub>DD3</sub> Linear Regulator   | This is a VDD3 regulator output feedback pin.  This pin is also the output of the V <sub>DD3</sub> standby regulator. |

| 29         | VDD3_B            | Analog<br>Output | VDD3 Linear<br>Regulator Base Drive | This pin can be used also as an additional standby regulator without the external pass transistor.                    |

| 30         | GND               | Ground           | Ground                              | This pin is a ground.                                                                                                 |

| 31         | VIGN              | Analog Input     | Voltage Ignition                    | This pin is the ignition switch control input pin. It contains an internal protection diode.                          |

| 32         | P3 <sup>(1)</sup> | Logic Input      | Programming Pin 3                   | Programming pin 3 for the $V_{DD3}$ , $V_{DDL}$ , and $V_{KAM}$ reference voltages.                                   |

#### Notes

<sup>1.</sup> Programming pins must never be left floating, they must be tied to ground or protected battery voltage depending on the output voltage selections desired.

# **ELECTRICAL CHARACTERISTICS**

# **MAXIMUM RATINGS**

#### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                                                                                                                | Symbol                              | Value                          | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------|------|

| Supply Voltage (VBAT)                                                                                                                                                                                  | V <sub>BAT</sub>                    | -0.3 to +40                    | V    |

| Keep-Alive Supply Voltage (KA_VBAT)                                                                                                                                                                    | KA_V <sub>BAT</sub>                 | -18 to +40                     | V    |

| Control Inputs (VIGN, P1, P2, P3), PFD Output                                                                                                                                                          |                                     | -18 to +40                     | V    |

| Bootstrap Voltage (BOOT, SR) referenced to ground                                                                                                                                                      | V <sub>BOOT</sub>                   | -0.3 to +50                    | V    |

| Bootstrap Voltage (BOOT, SR) referenced to SW                                                                                                                                                          | V <sub>BOOT</sub> - V <sub>SW</sub> | -0.3 to +12                    | V    |

| Charge Pump Output Voltage (CP)                                                                                                                                                                        | V <sub>CP</sub>                     | -0.3 to +12                    | V    |

| Switch Node Voltage SW                                                                                                                                                                                 | V <sub>SW</sub>                     | -2.0 to +40                    | V    |

| Sensor Supplies (VREF1, VREF2)                                                                                                                                                                         | V <sub>REF</sub>                    | -1.0 to +26.5                  | V    |

| Sensor Supplies (VREF1, VREF2) Maximum Slew Rate                                                                                                                                                       | V <sub>REFMAXSR</sub>               | 2.0                            | V/µs |

| Regulator Voltages (V <sub>DDH</sub> ,V <sub>DD3</sub> , V <sub>DD3_B</sub> , V <sub>DDL</sub> ,V <sub>DDL_B</sub> , V <sub>KAM</sub> )                                                                | V <sub>REG</sub>                    | -0.3 to +7.0                   | V    |

| Open Drain Outputs (RSTH, RSTL, RST3, RSTKAM, IGN_ON)                                                                                                                                                  | V <sub>DD</sub>                     | -0.3 to +7.0                   | V    |

| Regon Input                                                                                                                                                                                            | V <sub>REGON</sub>                  | -0.3 to +7.0                   | V    |

| Analog Inputs (VCOMP, INV, FREQ, HRT)                                                                                                                                                                  | V <sub>IN</sub>                     | -0.3 to +3.0                   | V    |

| ESD Voltage <sup>(2)</sup> Human Body Model - HBM (all pins except BOOT, VDDL, RSTL) Human Body Model - HBM (Pins BOOT, VDDL, RSTL) Machine Model - MM (all pins) Charge Device Model - CDM (all pins) | V <sub>ESD</sub>                    | ±2000<br>±1500<br>±200<br>±750 | V    |

| Operational Package Temperature (Ambient Temperature)                                                                                                                                                  | T <sub>A_MAX</sub>                  | -40 to +125                    | °C   |

| Storage Temperature                                                                                                                                                                                    | T <sub>STO</sub>                    | -65 to +150                    | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(3), (4)</sup>                                                                                                                                      | T <sub>PPRT</sub>                   | Note 4                         | °C   |

| Maximum Junction Temperature                                                                                                                                                                           | $T_{J\_MAX}$                        | 150                            | °C   |

| Thermal Resistance, Junction to Ambient <sup>(5)</sup>                                                                                                                                                 | R <sub>0J-A</sub>                   | 41                             | °C/W |

| Thermal Resistance, Junction to Case <sup>(6)</sup>                                                                                                                                                    | R <sub>0J-C</sub>                   | 1.2                            | °C/W |

#### Notes

- 2. ESD testing is performed in accordance with the Human Body Model (HBM) (AEC-Q100-2), the Machine Model (MM) (AEC-Q100-003),  $R_{ZAP} = 0 \Omega$ ), and the Charge Device Model (CDM), Robotic (AEC-Q100-011).

- 3. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 4. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

- 5. Thermal resistance measured in accordance with EIA/JESD51-2.

- 6. Theoretical thermal resistance from the die junction to the exposed pad.

# **RECOMMENDED OPERATING CONDITIONS**

# **Table 4. Recommended Operating Conditions**

All voltages are with respect to ground unless otherwise noted.

| Parameter                                                                           | Value        | Unit |

|-------------------------------------------------------------------------------------|--------------|------|

| Supply Voltages (V <sub>BAT</sub> , KA_V <sub>BAT</sub> )                           | *6.0 to 26.5 | V    |

| Switching Regulator Output Current (I <sub>VDDH</sub> ) total, VBAT = 6.0 to 26.5 V | 0 to 2.0     | А    |

| V <sub>DD3</sub> Standby Output Current                                             | 0 to 15      | mA   |

| V <sub>KAM</sub> Standby Output Current                                             | 0 to 15      | mA   |

| V <sub>REF1,2</sub> Output Current                                                  | 0 to 100     | mA   |

| Switching Frequency Range                                                           | 100 to 500   | kHz  |

<sup>\*</sup> Tracks battery voltage from 6.0 down to 4.5 V.

# STATIC ELECTRICAL CHARACTERISTICS

**Table 5. Static Electrical Characteristic**

Characteristics noted under conditions 6.0 V  $\leq$  KA\_V<sub>BAT</sub> = V<sub>BAT</sub>  $\leq$  26.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C using the typical application circuit, unless otherwise noted.

| Characteristic                                                                                                                | Symbol                 | Min   | Тур  | Max   | Unit |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|------|-------|------|

| GENERAL                                                                                                                       |                        | •     |      | 1     | •    |

| Keep-Alive Start-up Voltage (at the KA_VBAT pin), VKAM Output Up                                                              | V <sub>KAM_STUP</sub>  | 4.5   | _    | _     | V    |

| Start-up Voltage (at the KA_VBAT pin), VDD3, VDD3 standby, VDDL Up                                                            | V <sub>STUP</sub>      | 4.5   | _    | _     | V    |

| Over-voltage Shutdown                                                                                                         |                        |       |      |       | V    |

| Voltage at KA_VBAT pin rising                                                                                                 | V <sub>SHDN_R</sub>    | 35    | _    | 42    |      |

| Under-voltage Lock-out                                                                                                        |                        |       |      |       | V    |

| Voltage at KA_VBAT pin falling                                                                                                | $V_{UVLO_{F}}$         | 3.6   | _    | 4.3   |      |

| Voltage at KA_VBAT pin rising                                                                                                 | $V_{UVLO_R}$           | 3.7   | _    | 4.4   |      |

| Under-voltage Lock-out Hysteresis <sup>(7)</sup>                                                                              | V <sub>UVLO_HYS</sub>  | _     | 0.1  | _     |      |

| Sleep Quiescent Current (Sleep mode)                                                                                          | ΙQ                     |       |      |       | μΑ   |

| $V_{IGN} = 0 \text{ V}, \text{ REGON} = 0 \text{ V}, I_{VKAM} = 0 \text{ mA}, V_{DD3} \text{ OFF}, V_{BAT} = 14.0 \text{ V},$ |                        | _     | _    | 500   |      |

| KA_V <sub>BAT</sub> = 14 V (P1=1, P2=1, P3=1)                                                                                 |                        |       |      |       |      |

| SWITCHING REGULATOR (VDDH)                                                                                                    |                        | II.   |      |       |      |

| Buck Converter Output Voltage                                                                                                 | $V_{DDH}$              |       |      |       | V    |

| V <sub>BAT</sub> = 6.0 to 26.5 V, I <sub>LOAD</sub> = 100 mA                                                                  |                        | 4.9   | 5.0  | 5.1   |      |

| $V_{BAT} = 26.5 \text{ to } 35 \text{ V}, I_{LOAD} = 100 \text{ mA}$                                                          |                        | 4.85  | 5.0  | 5.15  |      |

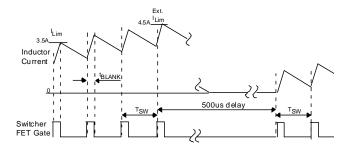

| Switching Regulator Current Limit (see Figure 5)                                                                              |                        |       |      |       | А    |

| Pulse-by-Pulse Current Limit                                                                                                  | I <sub>LIM_SW</sub>    | -2.25 | -3.5 | -4.25 |      |

| Extreme Current Limit (see Figure 5)(7)                                                                                       | I <sub>LIM_SW_EX</sub> | -3.75 | -4.5 | -6.00 |      |

| SW Drain Source On Resistance <sup>(7)</sup>                                                                                  | R <sub>DS(ON)</sub>    |       |      |       | mΩ   |

| $I_D = 500 \text{ mA}, V_{BAT} = 5.0 \text{ V}$                                                                               |                        | _     | _    | 200   |      |

| Thermal Shutdown Junction Temperature <sup>(7)</sup>                                                                          | TS <sub>H</sub>        | _     | _    | 195   | °C   |

|                                                                                                                               | TS <sub>L</sub>        | 155   | _    | _     |      |

| Thermal Shutdown Hysteresis <sup>(7)</sup>                                                                                    | TS <sub>HYS</sub>      | 1.0   | _    | 20    | °C   |

| VDD3 LINEAR REGULATOR                                                                                                         |                        |       |      |       |      |

| V <sub>DD3</sub> Output Voltage (Includes Line and Load Regulation)                                                           | $V_{DD3}$              |       |      |       | %    |

| I <sub>VDD3</sub> = 0 to -500 mA, See <u>Table 2</u> for V <sub>DD3</sub> Output Settings                                     |                        | -3.0  | _    | 3.0   |      |

| V <sub>DD3</sub> Dropout Voltage (V <sub>DDH</sub> - V <sub>DD3</sub> )                                                       | V <sub>DD3_DO</sub>    |       |      |       | V    |

| I <sub>VDD3</sub> = -800 mA (VDD3 set to 3.3 V via P1, P2, P3 and with an external transistor)                                | _                      | _     | 1.1  | 1.5   |      |

| $V_{DD3\_B}$ Current Limit, $V_{DD3\_B} = 0 V$ ,                                                                              | I <sub>VDD3B_Lim</sub> |       |      |       | mA   |

| KA_V <sub>BAT</sub> = 14 V, V <sub>BAT</sub> = 14 V                                                                           |                        | -20   | _    | -50   |      |

| $KA_{VBAT} = 5.0 \text{ V}, V_{BAT} = 5.0 \text{ V}$                                                                          |                        | -20   | _    | -50   |      |

Notes

7. Guaranteed By Design.

Table 5. Static Electrical Characteristic(continued)

Characteristics noted under conditions 6.0 V  $\leq$  KA\_V<sub>BAT</sub> = V<sub>BAT</sub>  $\leq$  26.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C using the typical application circuit, unless otherwise noted.

| Characteristic                                                                               | Symbol                   | Min  | Тур | Max | Unit |

|----------------------------------------------------------------------------------------------|--------------------------|------|-----|-----|------|

| VDD3 STANDBY LINEAR REGULATOR                                                                | 1                        |      | •   | •   | l    |

| V <sub>DD3</sub> Standby Output Voltage (Includes Line and Load Regulation)                  | V <sub>DD3_SBY</sub>     |      |     |     | %    |

| I <sub>VDD3_SBY</sub> = 0 to -15 mA, See <u>Table 2</u> for VDD3_SBY Output Setting          |                          | -15  | _   | 15  |      |

| V <sub>DD3</sub> Dropout Voltage (KA_V <sub>BAT</sub> - V <sub>DD3</sub> ) Standby Mode      | V <sub>DD3_DO</sub>      |      |     |     | V    |

| (VDD3 set at 3.3 V via P1, P2, P3) I <sub>VDD3</sub> = -10 mA                                |                          | _    | _   | 1.4 |      |

| V <sub>DD3</sub> Standby Current Limit, V <sub>DD3</sub> = 0 V                               | I <sub>VDD3SBY_LIM</sub> |      |     |     | mA   |

| $KA_{VBAT} = 14 \text{ V}, V_{BAT} = 14 \text{ V}$                                           |                          | -20  | _   | -50 |      |

| $KA_{VBAT} = 5.0 \text{ V}, V_{BAT} = 5.0 \text{ V}$                                         |                          | -20  | _   | -50 |      |

| Thermal Shutdown Junction Temperature <sup>(8)</sup>                                         | TS <sub>H</sub>          | _    | _   | 190 | °C   |

|                                                                                              | TS <sub>L</sub>          | 150  | _   | _   |      |

| Thermal Shutdown Hysteresis <sup>(8)</sup>                                                   | TS <sub>HYS</sub>        | 5.0  | _   | 20  | °C   |

| VDDL LINEAR REGULATOR                                                                        |                          |      |     |     |      |

| V <sub>DDL</sub> Output Voltage (Includes Line and Load Regulation)                          | $V_{DDL}$                |      |     |     | %    |

| $I_{VDDL}$ = 0 to -500 mA, See Table 1 for $V_{DDL}$ Output Setting                          |                          | -3.0 | _   | 3.0 |      |

| V <sub>DDL_B</sub> Dropout Voltage (V <sub>DDH</sub> - V <sub>DDL</sub> )                    | $V_{DDL\_DO}$            | _    | _   | 280 | mV   |

| (VDDL set at 3.3 V via P1, P2, P3) I <sub>VDDL</sub> = -800 mA                               |                          |      |     |     |      |

| V <sub>DDL_B</sub> Current Limit, V <sub>DDL</sub> = 0 V                                     | I <sub>VDDL_LIM</sub>    |      |     |     | mA   |

| $KA_{VBAT} = 14 \text{ V}, V_{BAT} = 14 \text{ V}$                                           |                          | -18  | _   | -50 |      |

| $KA_{VBAT} = 5.0 \text{ V}, V_{BAT} = 5.0 \text{ V}$                                         |                          | -18  | _   | -50 |      |

| VKAM STANDBY LINEAR REGULATOR                                                                | 1                        |      | •   | •   |      |

| V <sub>KAM</sub> Output Voltage (Includes Line and Load Regulation)                          | $V_{KAM}$                |      |     |     | %    |

| $I_{VKAM} = 0$ to -15 mA, See Table 1 for $V_{KAM}$ Output Setting                           |                          | -15  | _   | 15  |      |

| V <sub>KAM</sub> Dropout Voltage (KA_V <sub>BAT</sub> - V <sub>KAM</sub> )                   | V <sub>KAM_DO</sub>      |      |     |     | V    |

| $I_{VKAM} = -10 \text{ mA}, V_{KAM} \text{ set to } 5.0 \text{ V } (P1 = L, P2 = H, P3 = L)$ | _                        | _    | _   | 1.4 |      |

| VKAM STANDBY LINEAR REGULATOR (CONTINUED)                                                    | 1                        |      | •   | •   |      |

| V <sub>KAM</sub> Current Limit, V <sub>KAM</sub> = 0 V                                       | I <sub>VKAM_LIM</sub>    |      |     |     | mA   |

| KA_V <sub>BAT</sub> = 14 V, V <sub>BAT</sub> = 14 V                                          |                          | -20  | _   | -50 |      |

| $KA_{VBAT} = 5.0 \text{ V}, V_{BAT} = 5.0 \text{ V}$                                         |                          | -20  | _   | -50 |      |

| Thermal Shutdown Junction Temperature <sup>(8)</sup>                                         | TS <sub>H</sub>          | _    | _   | 190 | °C   |

|                                                                                              | TS <sub>L</sub>          | 150  | _   | _   |      |

| Thermal Shutdown Hysteresis <sup>(8)</sup>                                                   | TS <sub>HYS</sub>        | 5.0  | _   | 20  | °C   |

#### Notes

8. Guaranteed By Design.

Table 5. Static Electrical Characteristic(continued)

Characteristics noted under conditions 6.0 V  $\leq$  KA\_V<sub>BAT</sub> = V<sub>BAT</sub>  $\leq$  26.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C using the typical application circuit, unless otherwise noted.

| Characteristic                                                                                         | Symbol                                     | Min         | Тур         | Max                     | Unit |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------|-------------|-------------------------|------|

| SENSOR SUPPLIES VREF1, VREF2                                                                           |                                            |             | <u> </u>    |                         | I    |

| V <sub>REF</sub> On-resistance, I <sub>VREF</sub> = -100 mA                                            | R <sub>DS(ON)</sub>                        | _           | _           | 500                     | mΩ   |

| V <sub>REF</sub> Current Limit, V <sub>REF</sub> = -1.0 V <sup>(9)</sup>                               | I <sub>REF_LIM</sub>                       | -150        | -280        | -450                    | mA   |

| V <sub>REF</sub> Reverse Current Limit, V <sub>REF</sub> = 26.5 V <sup>(9)</sup>                       | I <sub>REF_REVLIM</sub>                    |             | _           | 40                      | mA   |

| V <sub>REF</sub> Leakage Current, V <sub>REF</sub> Shut Down, V <sub>REF</sub> = -1.0 V <sup>(9)</sup> | I <sub>REF_REVLIM</sub>                    | -2.0        | _           | _                       | mA   |

| Thermal Shutdown Junction Temperature <sup>(10)</sup>                                                  | TS <sub>H</sub><br>TS <sub>L</sub>         | <br>150     | _           | 190<br>—                | °C   |

| Thermal Shutdown Hysteresis <sup>(10)</sup>                                                            | TS <sub>HYS</sub>                          | 5.0         | _           | 20                      | °C   |

| SUPERVISORY AND CONTROL CIRCUITS                                                                       |                                            |             |             |                         |      |

| $V_{IGN}$ Input Voltage Threshold<br>$V_{BAT} = 14.0 \text{ V, } KA\_V_{BAT} = 14 \text{ V}$           | V <sub>IGN_IH</sub><br>V <sub>IGN_IL</sub> | 4.0<br>2.0  | 4.3<br>2.15 | 4.6<br>2.4              | V    |

| V <sub>IGN</sub> Hysteresis                                                                            | V <sub>IGN-HYS</sub>                       | 1.7         | _           | _                       | V    |

| $V_{IGN}$ Pull-down Current @ 5.0 V<br>$V_{BAT} = 14.0 \text{ V, KA}\_V_{BAT} = 14 \text{ V}$          | I <sub>PD</sub>                            | 10          | 30          | 60                      | μΑ   |

| REGON Input Voltage Threshold  V <sub>BAT</sub> = 14.0V, Battery Voltage = 14V                         | V <sub>IH</sub><br>V <sub>IL</sub>         | 1.7<br>-0.3 | _           | —<br>1.0                | V    |

| REGON Input Voltage Threshold Hysteresis                                                               | V <sub>IHYS</sub>                          | 0.1         | 0.3         | 0.4                     | V    |

| REGON Pull-down Current @ 3.0 V                                                                        | I <sub>PD</sub>                            | 5.0         | _           | 30                      | μΑ   |

| Programming Pin Input Voltage Threshold  V <sub>BAT</sub> = KA_V <sub>BAT</sub> = 14 V                 | V <sub>IH</sub><br>V <sub>IL</sub>         | 2.5<br>-0.3 | _<br>_      | V <sub>BAT</sub><br>1.0 | V    |

| Programming P1, P2, P3 Leakage Current @ 14.0 V                                                        | I <sub>PD</sub>                            | _           | 1.0         | 5.0                     | μA   |

| V <sub>DDH</sub> Reset Upper Threshold Voltage (ΔV <sub>DDH</sub> /V <sub>DDH</sub> )                  |                                            | 4.0         | 8.0         | 13.0                    | %    |

| V <sub>DDH</sub> Reset Lower Threshold Voltage (ΔV <sub>DDH</sub> /V <sub>DDH</sub> )                  |                                            | -3.0        | -8.0        | -13.0                   | %    |

| $V_{DDL}$ Reset Lower Threshold Voltage ( $\Delta V_{DDL}/V_{DDL}$ )                                   |                                            | -3.0        | -8.0        | -13.0                   | %    |

| $V_{DD3}$ Reset Lower Threshold Voltage ( $\Delta V_{DD3}/V_{DD3}$ )                                   |                                            | -3.0        | -8.0        | -13.0                   | %    |

| V <sub>DD3_SBY</sub> Reset Lower Threshold Voltage (ΔV <sub>DD3_SBY</sub> /V <sub>DD3_SBY</sub> )      |                                            | -3.0        | -12.5       | -30                     | %    |

| $V_{KAM}$ Reset Lower Threshold Voltage ( $\Delta V_{KAM} / V_{kAM}$ )                                 |                                            | -3.0        | -12.5       | -30                     | %    |

| RSTH, RSTL, RST3, RSTKAM Low-level Output Voltage I <sub>OL</sub> = 5.0 mA                             |                                            | _           | _           | 0.4                     | V    |

| IGN_ON Low-level Output Voltage I <sub>OL</sub> = 5.0 mA                                               |                                            | _           | _           | 0.4                     | V    |

#### Notes

<sup>9.</sup> The short circuit transient events on the VREF outputs must be limited to the voltage levels specified in the Maximum Ratings and slew rates of less than 2.0 V/µs, otherwise damage to the part may occur. Refer to the paragraph Sensor Supplies (VREF1, VREF2) on page 18 and typical application circuit diagrams on Figure 8 for recommended VREF output termination.

<sup>10.</sup> Guaranteed by design.

# **DYNAMIC ELECTRICAL CHARACTERISTICS**

# **Table 6. Dynamic Electrical Characteristics**

Characteristics noted under conditions 6.0 V  $\leq$  KA\_V<sub>BAT</sub> = V<sub>BAT</sub>  $\leq$  26.5 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C using the typical application circuit, unless otherwise noted.

| Characteristic                                                                                                          | Symbol             | Min | Тур          | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------|-----|------|

| GENERAL                                                                                                                 |                    |     | I            | L   |      |

| Power On Reset Delay Time (HR Timer) (see <u>Table 8</u> ) (Time to RESET up after Regulator in regulation)             | t <sub>D_POR</sub> | 0   | _            | 68  | ms   |

| Power On Reset Delay Time (HR Timer) Accuracy (33 k resistor)                                                           |                    | 8.0 | _            | 12  | ms   |

| Programming Pin Latching Delay <sup>(11)</sup>                                                                          | t <sub>LD_P</sub>  | _   | 500          | _   | μs   |

| SWITCHING REGULATOR                                                                                                     |                    |     |              |     |      |

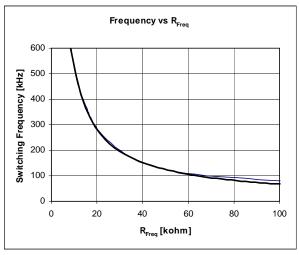

| Oscillator Frequency (Switching Freq.) Range - Adjustable (Figure 4)                                                    | Freq               | 100 | _            | 500 | kHz  |

| Oscillator Frequency Tolerance at 100 kHz (FREQ Pin Open)                                                               | f <sub>TOL</sub>   | 90  | _            | 110 | kHz  |

| SW Node Rise Time, $V_{BAT} = KA_{VBAT} = 14 \text{ V}$ , $I_{SW} = 500 \text{ mA}^{(11)}$ SR pin shorted to SW pin     | t <sub>SW_R</sub>  | _   | 0.96         | _   | V/ns |

| SR pin open SR pin shorted to BOOT pin                                                                                  |                    | _   | 1.82<br>2.38 |     |      |

| SW Node Fall Time, $V_{BAT} = KA_V_{BAT} = 14 \text{ V}$ , $I_{SW} = 500 \text{ mA}^{(11)}$<br>SR pin shorted to SW pin | t <sub>SW_F</sub>  |     | 0.83         | _   | V/ns |

| SR pin open SR pin shorted to BOOT pin                                                                                  |                    | _   | 0.83         | _   |      |

#### Notes

11. Guaranteed by design.

# **FUNCTIONAL DESCRIPTION**

#### **INTRODUCTION**

The 33730 multi-output power supply integrated circuit addresses the system power supply needs for applications using the Freescale 32-bit microcontroller family architecture.

#### **FUNCTIONAL PIN DESCRIPTION**

#### HARDWARE RESET TIMER (HRT)

This pin is the hardware reset timer input, which provides delays for the Reset outputs. This delay is programmed by an external resistor to GND.

#### **VKAM RESET (RSTKAM)**

This pin is an open drain reset output monitoring the  $V_{KAM}$  supply to the microprocessor. This output is actively pulled low when the VKAM output voltage falls below its reset threshold level.

# **VDDH RESET (RSTH)**

This pin is an open drain reset output monitoring the VDDH regulator. This output is actively pulled low when the VDDH output voltage falls below its reset lower threshold level or when the VDDH output voltage exceeds its reset upper threshold level

# **VDDL RESET (RSTL)**

This pin is an open drain reset output monitoring the VDDL regulator. This output is actively pulled low when the VDDL output voltage falls below its reset threshold level.

# **VDD3 RESET (RST3)**

This pin is an open drain reset output monitoring the VDD3 regulator. This output is actively pulled low when the VDD3 output voltage falls below its reset threshold level.

# **VREF OUTPUT 2 (VREF2)**

This pin is output of the protected supply VREF2. This output supplies sensors outside of the electronic control module and therefore it is protected against a battery short and short to -1.0 V. This pin is supplied from the  $V_{DDH}$  through the internal protection FET.

#### **VDDL REGULATOR (VDDL)**

This pin is the  $V_{DDL}$  regulator output feedback pin. The emitter of VDDL regulator external NPN pass transistor is connected to this pin.

### **VDDH REGULATOR (VDDH)**

This pin is the 5.0 V output feedback pin of the buck regulator. This pin is also a power input for the protected outputs VREF1 and VREF2.

#### VDDL REGULATOR BASE DRIVE (VDDL B)

VDDL linear regulator base drive. This output supplies current into the base of the regulator external pass NPN transistor.

#### **VREF OUTPUT 1 (VREF1)**

This pin is output of the protected supply VREF1. This output supplies sensors outside of the electronic control module and therefore it is protected against short battery and short to -1.0 V. This pin is supplied from the V<sub>DDH</sub> through the internal protection FET.

# REGULATOR HOLD ON (REGON)

Regulator Hold On input control pin. The 33730 can be enabled or kept in the Normal operational mode by holding this pin high. This is a 5.0 V logic input.

# VIGN STATUS (IGN ON)

This open drain output signals the status of the VIGN pin. This logic output is actively pulled low when the VIGN control input is pulled high.

#### **COMPENSATION (VCOMP)**

This pin provides switching pre-regulator compensation network. It is the output of the switching regulator error amplifier.

#### **INVERTING INPUT (INV)**

This pin is the inverting input of the switching regulator error amplifier.

# FREQUENCY ADJUSTMENT (FREQ)

This is the frequency adjustment input of the switching regulator. The operating frequency of the switching regulator can be programmed by an external resistor from this pin to ground.

#### **PROGRAMMING PIN 1 (P1)**

Programming Pin 1 for the VDD3, VDDL, and VKAM reference voltage. The output voltage of the VDD3, VDDL and VKAM regulators can be programmed by the P1, P2, and P3 pins (see <u>Table 7</u>).

#### **PROGRAMMING PIN 2 (P2)**

Programming Pin 2 for the VDD3, VDDL, and VKAM reference voltage. The output voltage of the VDD3, VDDL and VKAM regulators can be programmed by the P1, P2, and P3 pins (see <u>Table 7</u>).

#### **PROGRAMMING PIN 3 (P3)**

Programming Pin 3 for the VDD3, VDDL, and VKAM reference voltages. The output voltage of the VDD3, VDDL and VKAM regulators can be programmed by the P1, P2, and P3 pins (see <u>Table 7</u>).

# PROTECTION FET DRIVE (PFD)

Reverse battery protection FET gate drive. This pin is an output drive for the gate of the external Reverse Battery Protection N-channel FET.

# **BOOTSTRAP (BOOT)**

This pin is connected to the bootstrap capacitor. It provides the supply power for the switching regulator high-side drive.

#### SLEW-RATE (SR)

Slew-rate Control of the switching regulator. The slew-rate of the switching regulator can be adjusted by connecting this pin to switch node (SW pin, slow slew-rate selection), BOOT pin (fast slew-rate selection), or it can be left open (medium slew-rate selection).

### SWITCH NODE (SW)

This pin is the source of the switching regulator internal power switch (N-channel MOSFET source).

#### **BATTERY VOLTAGE SUPPLY (VBAT)**

Voltage supply to the IC (external reverse battery protection is recommended).

#### **KEEP ALIVE SUPPLY (KA VBAT)**

This pin is the keep alive supply input. This input is reverse battery protected. This input supplies power to the internal supply and bias circuits that have to do with this VKAM and other always-on supplies.

#### **CHARGE PUMP (CP)**

External reservoir capacitor of the internal charge pump. This charge pump provides the voltage needed to sufficiently enhance the gates of the internal n-channel mosfets (VREF1, VREF2, and VDDH) during the low battery condition.

# **KEEP ALIVE MEMORY (VKAM)**

Keep Alive Memory (standby) supply output. This output supplies power for the module Keep-Alive memory. This output is always on, if the voltage at the KA\_VBAT pin is above 4.5 V.

#### VDD3 LINEAR REGULATOR (VDD3)

This is a VDD3 regulator output feedback pin. The emitter of VDD3 regulator external NPN pass transitory is connected to this pin.

This pin can programmed to be the output of the VDD3 Standby regulator (see <u>Table 7</u>).

# VDD3 LINEAR REGULATOR BASE DRIVE (VDD3\_B)

This pin can be used also as an additional standby regulator without the external pass transistor. This output supplies current into the base of the regulator external pass NPN transistor.

#### **GROUND (GND)**

This pin is the ground pin of the integrated circuit.

# **VOLTAGE IGNITION (VIGN)**

This pin is the turn-on control input that is controlled through an ignition switch. This pin is reverse battery protected.

#### FUNCTIONAL INTERNAL BLOCK DESCRIPTION

#### **5.0 VOLT BUCK REGULATOR**

This is the main regulator that supplies 5.0 Volts to the following protected and regulated outputs, VREF1, VREF2, VDD3, and VDDL.

#### **OSCILLATOR**

This is the frequency source for the switching (buck) 5 Volt regulator. The frequency of oscillation is selected by an external resistor to ground.

#### **BAND GAP REFERENCE**

This is the main voltage reference, which is used as the standard for all the current and voltage sources in the MC33730.

#### PROTECTION FET DRIVER

The protection FET is used to prevent reverse battery connections from damaging the MC33730. The gate drive for the Protection FET is provided by this driver circuit.

### SLEEP/WAKE CIRCUITRY

This circuitry is responsible for the two main modes of operation for the MC33730, Sleep mode and Wake mode. In the Sleep mode, only the keep alive outputs are active, and the rest of the circuitry is in a low power drawing sleep state. In the Wake mode, the MC33730 is fully functional and normal current is being consumed.

#### **IGNITION DRIVER**

This block of circuitry controls all the voltage outputs, except for the keep alive voltage output(s). It also provides an

output signal to indicate that the ignition switch has been activated.

#### VREF1

This output is one of two protected 5.0 volt outputs that can be used to supply external sensors or other analog circuits requiring a regulated, short-circuit protected 5.0 volt supply.

#### VREF2

This output is one of two protected 5.0 volt outputs that can be used to supply external sensors or other analog circuits requiring a regulated, short-circuit protected 5.0 volt supply.

#### **VDD3 REGULATOR**

This is one of three, voltage programmable, regulated supplies. This supply is controlled by the ignition switch.

#### **VDDL REGULATOR**

This is one of three, voltage programmable, regulated supplies. This supply is controlled by the ignition switch.

#### **VKAM**

This is one of three, voltage programmable, regulated supplies. This supply is NOT controlled by the ignition switch.

#### **VOLTAGE PROGRAMMING**

P1, P2, and P3 are three logic level inputs that control the voltage that is available on the VDD3, VDDL and VKAM outputs.

<u>Table 7</u> indicates the 8 different combinations of P1, P2, and P3 and the resultant voltage values.

# **RESET CIRCUITRY**

There are four open drain reset lines that indicate the status of the four voltage outputs; VDDH, VDDL, VDD3, and VKAM. They are labeled: RSTH, RSTL, RST3, and RSTKAM.

# **REGON INPUT**

This input is OR'd with VIGN. However, it is a 5.0 volt logic input, as opposed to VIGN, which is a  $\rm V_{BAT}$  level input. This input is controlled by an MCU I/O pin, to hold power up when the ignition switch is turned off, so housekeeping functions can be performed before power is shut off, by lowering the REGON line. IF REGON is not needed, it should be tied to GND.

# **FUNCTIONAL DEVICE OPERATION**

#### **OPERATION DESCRIPTION**

#### INTRODUCTION

The 33730 has two supply inputs. The KA\_VBAT pin is the supply input for the standby regulators  $V_{KAM}$  (and optionally  $V_{DD3\_SBY,}$  see  $\underline{Table~7}$ ) and for the internal supply circuits. The VBAT pin is the power input of the integrated buck regulator, which steps-down the protected battery voltage providing directly the 5.0 V system supply  $V_{DDH}.$   $V_{DDH}$  provides power for the main linear regulator(s)  $V_{DDL},$   $V_{DD3},$  and also for the other module circuits requiring 5.0 V supply voltage (e.g. protected  $V_{REF1.2}$  outputs).

If the supply voltage ramps from zero volts up to its nominal level, the 33730 will start at the latest when the supply (battery) voltage reaches  $\rm V_{STUP}$  at the KA\_VBAT pin. If the supply voltage ramps down, the 33730 will keep operating (with degradation of the output voltage regulation) down to  $\rm V_{UVLO_f}$  at the KA\_VBAT pin. The  $\rm V_{KAM}$  output stays operational down to  $\rm V_{UVLO_f}$  at the KA\_VBAT pin.

The 33730 will operate in systems with and without standby mode. In the Standby (sleep) mode of operation the IC will draw maximum  $I_Q$  quiescent current, assuming only the VKAM is used as a standby output, and it is unloaded. When VDD3 is used as an additional standby output the quiescent current increases by approximately another 100  $\mu$ A.

# **POWER UP**

The 33730 will safely power up when the power is applied simultaneously (hot plugged) or in the random sequence to the KA\_VBAT, VBAT and VIGN (or REGON) inputs.

### **POWER DOWN**

The 33730 will safely power down when the power is disconnected from any of the KA\_VBAT, VBAT inputs or when control signals the VIGN or REGON inputs go low.

#### **UNDERVOLTAGE LOCK-OUT (UVLO)**

There is an under-voltage lock-out feature implemented into the IC. When the battery voltage at the KA\_VBAT pin falls below  $V_{\text{UVLO}\_f}$  the under-voltage comparator initiates the power down sequence for the whole IC. The under-voltage lock-out circuit has a  $V_{\text{UVLO}\_hys}$  hysteresis and 5.0  $\mu s$  glitch filter in order to prevent spurious tripping its threshold level and consequent system oscillations between the ON and OFF states.

#### SWITCHING REGULATOR

The 33730 switching regulator is a fixed frequency (externally adjustable) PWM voltage mode controller with integrated low- $R_{DS(ON)}$  N-channel power MOSFET. This architecture is widely flexible and provides a possibility to

optimize its operation over a wide range of input voltages. The 33730 switching regulator provide the following features:

#### **Adjustable Switching Frequency**

The adjustable frequency feature provides the ability to modify the switcher performance for optimized cost (higher frequency, smaller, cheaper components), or higher efficiency and better EMC performance (lower switching frequency for reduced losses and EMI). The operating frequency of the switching regulator can be adjusted by means of an external resistor  $R_F$  connected from the FREQ pin to ground (see Figure 4).

$F_{SW} \cong 18.48 + (5098.7/R_{FREQ})$  $F_{SW i}$ s the switch frequency in kHz

R<sub>FREQ</sub> is the resistor value in kOhms

Figure 4. Switching Regulator Frequency vs. R<sub>Freq</sub> Value

#### Adjustable Slew-rate

The adjustable slew-rate option allows, with selection of the right switching frequency, optimization of the system for EMC performance.

#### Over-voltage Lock-Out (Shutdown)

The over-voltage lock-out (shutdown) feature turns the switching regulator off when the input voltage exceeds the  $V_{SHDN\_r}$  limit. This extends the 33730 capability to survive the severe load dump conditions up to max  $V_{BAT}$ .

# Operation at 100% Duty Cycle

The internal charge pump is used to enhance the power MOSFET gate when the switching regulator reaches 100% duty cycle during the low battery conditions.

The switching regulator output voltage  $V_{DDH}$  is regulated to provide 5.0 V @ 2.0 A with  $\pm 2\%$  accuracy and it is intended

to directly power the digital and analog circuits of the Electronic Control Module (ECM). The switching regulator output current is also used by the following linear regulators  $V_{DD3\_3}$ ,  $V_{DDL}$ , and sensor supplies  $V_{REF1}$ , and  $V_{REF2}$ .

The direct voltage conversion to  $V_{DDH} = 5.0 \text{ V}$  together with the Protection FET Driver circuit allows operation of the IC at very low battery voltages, which would otherwise require to use a boost regulator (with an additional system cost) or a different and more expensive switching converter topology (e.g. flyback).

#### **Short Circuit Protection**

The switching regulator is protected against the overcurrent and short-circuit conditions. It integrates a current limit circuit, which has two threshold levels - the pulse by pulse, and the extreme.

#### **Pulse by Pulse Current Limit**

Pulse-by-Pulse Current Limit threshold has a nominal value set I<sub>LIM\_SW</sub>. When the current flowing through switching regulator power FET exceeds this value the power FET is immediately turned off. During the next switching cycle the power FET is turned on again until it is commanded off by its natural duty cycle or until the current reaches the threshold level again. It should be noted that the current limit is blanked for several tens of nanoseconds during the turn-on and turn-off transition times in order to prevent erroneous turn off due to the current spikes caused by switcher parasitic components.

#### **Extreme Current Limit.**

In some cases, during the over-current or short-circuit condition, the inductor current does not sufficiently decay during the off time of the switching period. The current rise during the current limit blanking time is higher than the decay during the off time. In this case the current in the inductor builds up every consecutive switching cycle. In order to prevent the power FET failure during this condition an extreme current limit has been implemented. When the current flowing through the power FET reaches the  $I_{\text{LIM\_SW\_Ext}}$  threshold, the switching regulator will shut off for 500  $\mu$ s, before the switching regulator is allowed to turn on again (see Figure 5).

Figure 5. 33730 Current Limit

#### Soft Start

The switching regulator has an integrated soft-start feature. During the soft-start sequence the duty cycle of the internal power switch will be gradually increased from low value to the regulation level. This technique prevents any undesirable inrush current into the buck regulator output capacitor.

#### LINEAR REGULATORS

The 33730 integrates two linear regulator control circuits  $V_{DD3}$  (programmable),  $V_{DDL}$  (programmable) both capable of driving up to 15 mA (min.) base current into the external pass NPN transistors. The output voltage of both linear regulators is monitored at their feedback pins ( $V_{DD3}$  and  $V_{DDL}$ ). If the voltage at any of the  $V_{DD3}$ ,  $V_{DDL}$  feedback pins fall below their regulation level, the supervisory Reset control circuits will assert the corresponding reset signal (RSTL, and/or RST3 lines will be pulled low). See Table 7 for the output voltage selection details.

The linear regulators will stay in regulation down to 4.5 V at the KA\_VBAT pin.

The 33730 linear regulators offer high flexibility and variability of the module design in terms of selectable output voltages as well as wide range of output current capability. There several types of suitable external pass NPN transistors which could be used. The choice of the particular type depends mostly on the expected power dissipation of the pass transistor. The following parts provide good solution and have been bench tested with the 33730:

BCP68T1 (SOT-223)

NJD2873T4 (DPAK)

MJB44H11 (D<sup>2</sup>PAK)

Available from ON Semiconductor.

**NOTE:** The 33730 linear regulators have been designed to use low ESR ceramic output capacitors - see <u>Figure 8</u> and <u>Figure 9</u> for the recommended values.

#### STANDBY REGULATORS

The 33730 integrates two standby linear regulators, the  $V_{KAM}$  and the optional standby regulator  $V_{DD3}$  (see Figure 9) for the optional standby circuit). The output voltage levels of both standby linear regulators are programmable and supervised by the Reset control circuits (RSTKAM, and/or RST3). Both the  $V_{KAM}$  and  $V_{DD3}$  outputs are capable of delivering  $I_{VKAM\_LIM}$  and  $I_{VDD3\_LIM}$  of load current. See Table 7 for the  $V_{KAM}$  and  $V_{DD3}$  standby output voltage selection details.

The  $V_{KAM}$  standby regulator will keep functioning even below  $V_{UVLO\_f}$  but the specified drop out voltage may not be maintained.

**NOTE:** The 33730 standby regulators have been designed to use low ESR ceramic output capacitors - see <u>Figure 8</u> and <u>Figure 9</u> for recommended values.

# PROGRAMMING LINEAR REGULATOR OUTPUT VOLTAGE

The output voltage of the VDD3, VDDL and VKAM outputs can be externally programmed by placing logic levels on the programming pins P1, P2, and P3 (see <u>Table 7</u>). This extends the application flexibility of the IC without having to use an external resistor divider, thus improving the regulator accuracy over the whole temperature range, and reducing the component count.

The logic level of the programming pin (Px) can be selected by tying the pin to ground (logic level "0") or to protected battery voltage (logic level "1"). Programming pins must never be left floating, they must be tied to either ground or protected battery voltage.

The programming information is read and latched with the 500 µs delay after the power is applied to the IC.

Table 7. Programming VDD3, VDDL, VKAM Output Voltage

| P1   | P2   | P3   | <b>V</b> <sub>DD3</sub> | $\mathbf{v}_{DDL}$ | V <sub>KAM</sub> |

|------|------|------|-------------------------|--------------------|------------------|

| High | High | High | 3.3 V                   | 2.6 V              | 2.6 V            |

| High | High | Low  | 3.3 V                   | 3.3 V              | 3.3 V            |

| High | Low  | High | 3.3 V                   | 1.5 V              | 1.0 V            |

| High | Low  | Low  | 3.3 V                   | 3.3 V              | 1.0 V            |

| Low  | High | High | 3.3 V Standby           | 3.3 V              | 1.0 V            |

| Low  | High | Low  | 2.0 V                   | 3.15 V             | 5.0 V            |

| Low  | Low  | High | 2.6 V Standby           | 3.3 V              | 1.0 V            |

| Low  | Low  | Low  | 2.6 V Standby           | 3.3 V              | 1.5 V            |

The Programming Pins can be tied high, to protected battery voltage, or low, to ground.

#### LOW BATTERY OPERATION

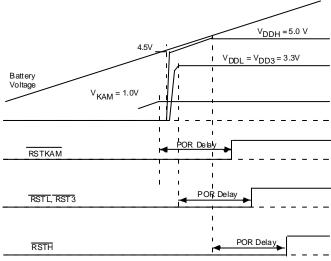

When the battery voltage falls below the specified minimum value, the 33730 switching regulator will enter a 100% duty cycle mode of operation and its output voltage  $V_{DDH}$  will follow the decreasing battery voltage. If the battery voltage continues to fall, the  $V_{DDH}$  voltage reaches its reset threshold level, and the RSTH signal will be pulled low, but the other linear regulators will continue to operate, and their monitoring signals stay high as long as the VDDH provides sufficient headroom for the regulators to stay in their regulation limits (see Figure 6 and Figure 7). If the battery voltage continues to fall, the linear regulators would not have sufficient headroom to stay in regulation, and their resets would be asserted (RSTL, RST3, or both would be pulled low). At that moment the power down sequence would be engaged.

The  $V_{KAM}$  standby regulator will operate down to ( $V_{KAM \text{ and}}$   $V_{KAM\_DO}$ ) and  $V_{KAM-DO}$  at the KA\_VBAT pin.

#### POWER SEQUENCING (VDDH, VDD3, VDDL)

$\rm V_{DDH},\,V_{DD3},$  and  $\rm V_{DDL}$  are power sequenced by means of internal pull-down FETs. During the power up sequence,  $\rm V_{DD3}$  and  $\rm V_{DDL}$  will follow  $\rm V_{DDH}.$

During the power down sequence the VDD3 and VDDL outputs will be pulled down by the internal pull-down power FETs, and  $V_{DDH}$  will be shut off with a defined delay (~100  $\mu$ s typ.).

In order to engage the power down sequence, the following conditions have to be met:

$(\overline{VIGN} \cdot \overline{REGON}) + \overline{UVLO} = Power Down$

The VDD3 output is not power sequenced when used as a standby regulator.

#### **SENSOR SUPPLIES (VREF1, VREF2)**

There are two sensor supplies, VREF1 and VREF2, integrated into the IC. They are internally connected to  $V_{DDH}$  through power MOSFETs which protect against short to battery and short to ground conditions.

Severe fault conditions on the VREF1 and VREF2 outputs, like shorts to either ground or battery, will not disrupt the operation of the main regulator  $V_{DDH}$ , or cause assertion of any Reset signal.

#### IMPORTANT NOTE:

The VREF outputs MUST be externally protected against transient voltage events with slew rates faster than 2.0 V/ $\mu$ s, otherwise damage to the part may occur. A practical and inexpensive solution consists of using a series RC network connected from the VREF output to ground (see Figures 8 and 9 for typical component values). Other means, such as a single electrolytic capacitor with its capacitance value C > 10  $\mu$ F, may be also used.

#### PROTECTION FET DRIVE (PFD)

The Protection FET Drive circuit allows using an optional N-channel protection MOSFET (instead of a standard reverse protection diode) to protect against a reverse battery voltage condition. This approach improves the operating capabilities at very low battery voltages.

An internal **charge pump** is used to enhance the Protection FET gate during nominal and low battery conditions. The charge pump will be enabled at the startup voltage. When the battery voltage gets sufficiently high, the Protection FET is turned off and the integrated circuit power input (VBAT pins) are supplied through the body diode of the Protection FET.

Use of the Protection FET is not necessary in systems already using a protection diode, relay or when no reverse battery protection is required.

#### **CONTROL INPUT (VIGN)**

The VIGN pin is used as a control input to the IC. The regulation circuits will function and draw current from  $V_{BAT}$  when  $V_{IGN}$  is high (active) or when the REGON pin is high. The VIGN pin has a  $V_{IHN-IH}$  power-up threshold  $V_{IGN-IL}$  typical power-down threshold) and  $V_{IGN-HYS}$  (minimum) of hysteresis.  $V_{IGN}$  is designed to operate up to max  $V_{BAT}$  battery while providing reverse battery and max  $V_{BAT}$  load dump protection.

#### **REGON**

The REGON feature permits the microcontroller to select a delayed shutdown of the 33730. It holds off the activation of the reset signals to the microcontroller after the  $V_{\rm IGN}$  signal has transitioned. This allows the microcontroller to control the power up and power down of the main regulator outputs except for the standby supplies. The REGON pin input threshold voltages allow control by the standard 2.5 V (up to 5.0 V) logic ICs.

# HARDWARE RESETS (RSTL, RST3, RSTH, and RSTKAM)

The Hardware Resets are open drain, active low outputs capable of sinking 5.0 mA current and able to withstand +7.0 V.

The  $\overline{\text{RSTL}}$  control circuit monitors the  $V_{DDL}$  output. If the  $V_{DDL}$  output is out of regulation (low), the device will assert the RSTL signal low.

The  $\overline{\text{RST3}}$  control circuit monitors the V<sub>DD3</sub> output. If the V<sub>DD3</sub> output is out of regulation (low), the device will assert the RST3 signal low.

The  $\overline{\text{RSTH}}$  control circuit monitors the  $V_{DDH}$  output. If the  $V_{DDH}$  output is out of regulation (low or high), the device will assert the  $\overline{\text{RSTH}}$  signal low.

The RSTKAM control circuit monitors the  $V_{KAM}$  output. If the  $V_{KAM}$  output is out of regulation (low), the device will assert the RSTH signal low.

All Reset monitoring circuits have a 20  $\mu s$  delay filter to avoid unintended resets caused by noise glitches on the regulator output lines.

#### **HR TIMER**

The HR (Hardware Reset) Timer provides the delay between the time when the particular regulator output voltage is in regulation and the release of the Reset signal. This delay can be programmed by a single external resistor. This solution provides better accuracy than the commonly used external RC timer. The HR Timer delay can be programmed in eight 8ms steps from 0 to 56 ms (see Table 8)

**Table 8. HR Timer Delay Programming**

| Programming Resistor<br>Value R <sub>HRT</sub> [ohms] | Delay (typ.) [ms] |

|-------------------------------------------------------|-------------------|

| 68 k                                                  | 0                 |

| 33 k                                                  | 10                |

| 16 k                                                  | 19                |

| 8.2 k                                                 | 29                |

| 3.9 k                                                 | 39                |

| 2.0 k                                                 | 48                |

| 1.0 k                                                 | 58                |

| 470                                                   | 68                |

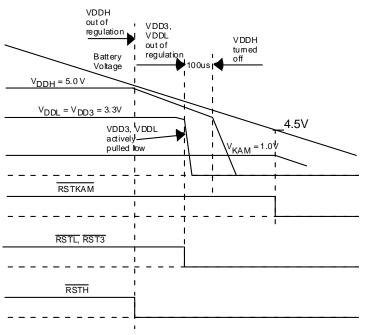

Figure 6. Battery Voltage Ramp Up

Figure 7. Battery Voltage Ramp Down

#### **OPERATIONAL MODES**

The 33730 can operate in the two modes: Low quiescent current Sleep mode and Normal mode of operation.

### **SLEEP MODE**

The 33730 operates in the Sleep mode when both the VIGN pin and the REGON pins are pulled low. Both of these pins have internal pull-downs, which assures that the IC is in this defined state when those pins are left open.

When the IC enters the Sleep mode, all major functions are disabled except for the Standby regulators. The Keep-Alive regulator VKAM stays always operational (see  $\underline{\text{Table 7}}$ ). If this output stays unloaded, the IC in the Sleep mode consumes very low quiescent current (I $_{\!Q}$ ).

If the VDD3 output was programmed as a VDD3 Standby regulator (see <u>Table 7</u>), it too stays operational during the

Sleep mode, as well as the VKAM regulator. In this case, the IC consumes about 100  $\mu$ A of additional quiescent current (assuming both VKAM and VDD3 Standby outputs are unloaded).

NOTE: In the Sleep mode, the RSTKAM and RST3 are not active and their outputs (as well as the outputs of RSTL and RSTH) are in the high-impedance state.

#### NORMAL MODE

The 33730 enters the Normal mode of operation when either the VIGN pin or the REGON pin is pulled high. In this case the IC is fully operational with all regulator outputs ready to supply power and all control, monitoring and protection features activated.

# TYPICAL APPLICATIONS

#### Notes

- 12. The  $V_{\mbox{\scriptsize DDH}}$  total current includes the sum of all output currents of the IC.

- 13. Higher resistance (60 k) and higher capacitance (4.7nF) in the compensation network will reduce the V<sub>DDH</sub> overshoot. Compensation network values should be optimized for specific circuit applications.

Figure 8. 33730 Typical Application Circuit

Table 9. Programming Output Voltage (BOLD denotes selected combinations)

| P1   | P2   | P3   | V <sub>DD3</sub> | <b>V</b> <sub>DDL</sub> | V <sub>KAM</sub> |

|------|------|------|------------------|-------------------------|------------------|

| High | High | High | 3.3 V            | 2.6 V                   | 2.6 V            |

| High | High | Low  | 3.3 V            | 3.3 V                   | 3.3 V            |

| High | Low  | High | 3.3 V            | 1.5 V                   | 1.0 V            |

| High | Low  | Low  | 3.3 V            | 3.3 V                   | 1.0 V            |

| Low  | High | High | 3.3 V Standby    | 3.3 V                   | 1.0 V            |

| Low  | High | Low  | 2.0 V            | 3.15 V                  | 5.0 V            |

| Low  | Low  | High | 2.6 V Standby    | 3.3 V                   | 1.0 V            |

| Low  | Low  | Low  | 2.6 V Standby    | 3.3 V                   | 1.5 V            |

Notes

- 14. The  $V_{DDH}$  total current includes the sum of all output currents of the IC.

- 15. Higher resistance (60 k) and higher capacitance (4.7nF) in the compensation network will reduce the V<sub>DDH</sub> overshoot. Compensation network values should be optimized for specific circuit applications.

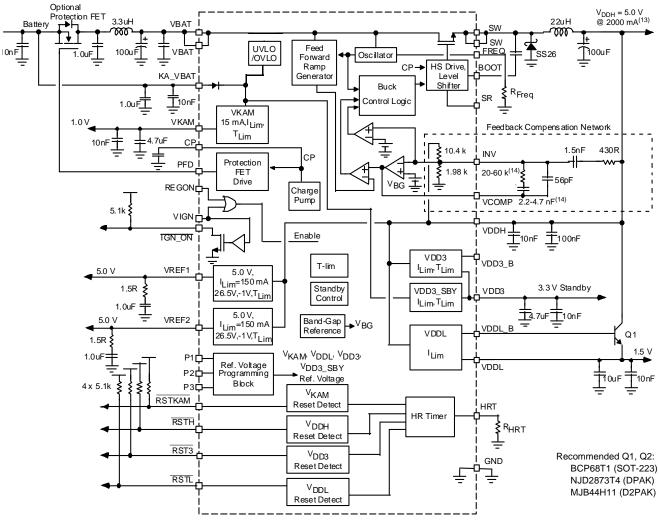

Figure 9. 33730 Typical Application, VDD3 Standby Output @ 15 mA

Table 10. Programming Output Voltage (BOLD denotes selected combinations)'

| P1   | P2   | P3   | V <sub>DD3</sub> | <b>V</b> <sub>DDL</sub> | V <sub>KAM</sub> |

|------|------|------|------------------|-------------------------|------------------|

| High | High | High | 3.3V             | 2.6V                    | 2.6V             |

| High | High | Low  | 3.3V             | 3.3V                    | 3.3V             |

| High | Low  | High | 3.3V             | 1.5V                    | 1.0V             |

| High | Low  | Low  | 3.3V             | 3.3V                    | 1.0V             |

| Low  | High | High | 3.3 V Standby    | 3.3 V                   | 1.0 V            |

| Low  | High | Low  | 2.0 V            | 3.15 V                  | 5.0 V            |

| Low  | Low  | High | 2.6 V Standby    | 3.3 V                   | 1.0 V            |

| Low  | Low  | Low  | 2.6 V Standby    | 3.3 V                   | 1.5 V            |

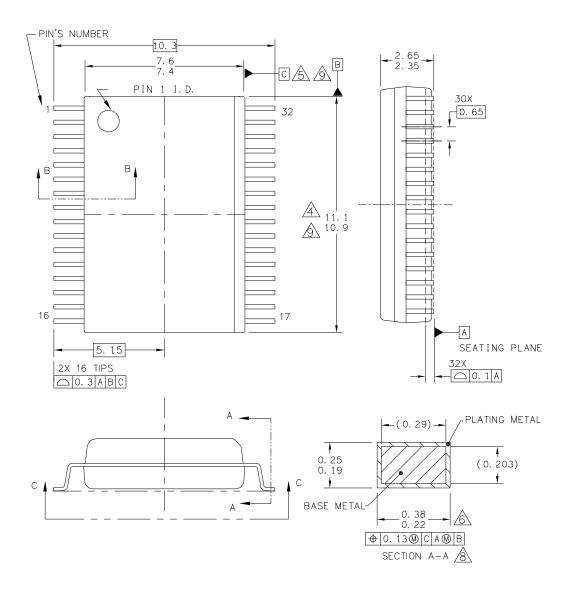

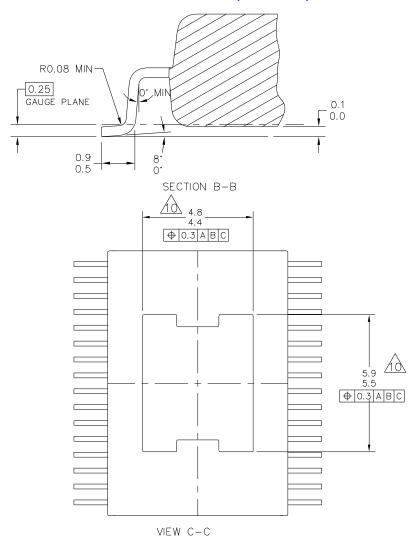

# **PACKAGING**

# **PACKAGE DIMENSIONS**

For the most current package revision, visit <u>www.freescale.com</u> and perform a keyword search using the 98ARL10543D listed below. Dimensions shown are provided for reference ONLY.

| © FREESCALE SEMICONDUCTOR, INC.  ALL RIGHTS RESERVED.  MECHANICA |              | L OUTLINE   | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------------------|--------------|-------------|------------------|-------------|

| TITLE: 32LD SOIC W/B, 0.6                                        | 5 PITCH      | DOCUMENT NO | : 98ARL10543D    | REV: C      |

| 5.7 X 4.6 EXPOSE                                                 | CASE NUMBER  | 2: 1437-03  | 08 MAY 2008      |             |

| CASE OUTLINE                                                     | STANDARD: NO | N-JEDEC     |                  |             |

EK SUFFIX (PB-FREE) 32-PIN SOICW - EP 98ARL10543D REVISION C

# PACKAGE DIMENSIONS (Continued)

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | DT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: 32LD SOIC W/B, 0.6                            | 55 PITCH  | DOCUMENT NO  | : 98ARL10543D    | REV: C      |

| 5.7 X 4.6 EXPOSE                                     |           | CASE NUMBER  | 2: 1437-03       | 08 MAY 2008 |

| CASE OUTLIN                                          | E         | STANDARD: NO | N-JEDEC          | •           |

EK SUFFIX (PB-FREE) 32-PIN SOICW - EP 98ARL10543D REVISION C

### **PACKAGE DIMENSIONS (Continued)**

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS B AND C TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

√5\ THIS DIMENSION DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS. INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

6. THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.4 mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT LESS THAN 0.07 mm.

/7. EXACT SHAPE OF EACH CORNER IS OPTIONAL.

THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 mm AND 0.3 mm FROM THE LEAD TIP.

$\cancel{ ext{(9)}}$  the package top may be smaller than the package bottom. This dimension is DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTER-LEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

THESE DIMENSIONS RANGES DEFINE THE PRIMARY KEEP-OUT AREA. MOLD LOCKING AND RESIN BLEED CONTROL FEATURES MAY BE VISIBLE AND THEY MAY EXTEND TO 0.9mm FROM MAXIMUM EXPOSED PAD SIZE

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA   | L OUTLINE    | PRINT VERSION NO | DT TO SCALE |

|------------------------------------------------------|-------------|--------------|------------------|-------------|

| TITLE: 32LD SOIC W/B, O.                             | 65 PITCH    | DOCUMENT NO  | ): 98ARL10543D   | REV: C      |

| 5.7 X 4.6 EXPOSE                                     | CASE NUMBER | R: 1437–03   | 08 MAY 2008      |             |

| CASE OUTLINE                                         |             | STANDARD: NO | N-JEDEC          |             |

**EK SUFFIX (PB-FREE)** 32-PIN SOICW - EP 98ARL10543D **REVISION C**

# **REFERENCE SECTION**

# **Table 11. Reference Documents**

| Reference | Description                             |

|-----------|-----------------------------------------|

| MC33730ER | MC33730, Mask DA03M89H, Rev. 4.2 Errata |

# **REVISION HISTORY**

| REVISION | DATE   | DESCRIPTION OF CHANGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.0      | 2/2009 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |